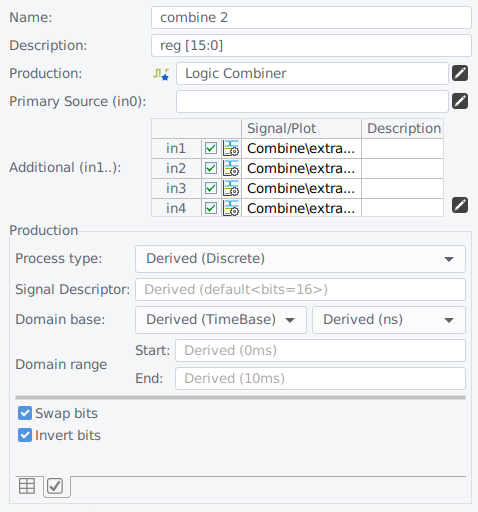

R032 Logic Combine Production

Outline

Combines multiple logic (1-dimensional or vectors) signals into one logic vector containing all bits.

| Platforms: |

|

|||

| Requirements: |

|

|||

| Known limitations: |

|

|||

| Status: |

|

|||

| Input signals: |

|

|||

| Output signal: |

|

|||

| Parameters: |

|

Input Signal Configuration

The production accepts 1..N Logic signal.

- Primary Source

- The primary source is the first source signal of the production. For productions with multiple inputs it can be left empty, thus the first input is taken from the "Additional" sources.

- Additional (Sources)

- If more than 1 source signal is required, add them into this table. Instead of using the table you may drag and drop (with a closed dialog) signals onto the plot item.

Output Signal Configuration

Productions are executed on the fly, as soon as the signal data is required for further processing, and re-executed when settings or input signal have been changed. Before executing a script, the system needs to know the source signals, the type and the domain of the signal. All these informations need to be entered into the plot configuration dialog. If you leave the configuration fields empty, impulse tries to extract the information from the sources. The fields will display this information in light gray <e.g. Derived(Time)>.

- Process type

- You may select between discrete and continuous process type.

- Signal descriptor

- The signal descriptor describes the signal type in more details (e.g the bit width of a logic vector (default<bits=16>)). See below for more details. But in most case, you will use the standard settings (default<>) - Press CTRL-Space to view content proposals.

- Domain Class/Base

- The domain base is just required if your output signal has a different domain than the source signals. If not, just don't touch these settings.

- Domain Range

- Use this field to set the domain range, so the minimum and maximum value of the domain (e.g. 0 .. 1000 Hz)

Production Configuration

- Swap: Check to swap bits.

- Invert:Check to invert bits.

You may check the "Swap" flag to swap the source bits (left-to-right) and/or the "Invert" flag to invert all bits.

The output signal is a Logic signal containing all bits of the input signals. The bits of first input signal will start at bit pos 0, all following signals will be added after (to the left).

Signal Handling

- Keep tags: The output samples shall keep the tag information of each input sample.

- Ignore 'None': Ignore 'None' samples of the input signals.

- Hide identical: Check to hide sequence of identical samples (will only write to output signal in case of changed sample value/tag, may not have any effect in case of 'Continuous' process type).

The signal handling flags give the user more control over the output signal generation. If the "Keep tags" is checked, the output samples will get the tag information of each input samples. The "Ignore None" flag let the production ignore 'None' input samples. The "Hide identical" hides the production from generating sequences of identical samples.

Operation

Below you find the operation code for the production.

// iterate

while (iter.hasNext() && !isCanceled()) {

// step

Long current = iter.next(targetWriter);

// iterate over inputs

int idx = 0;

boolean changed = false;

for (int n = 0; n < input.length; n++) {

// input

ISamplePointer pointer = input[n];

if (pointer != null) {

// pointer stepped ?

if (pointer.getIndex() > sourceIndex[n]) {

sourceIndex[n] = pointer.getIndex();

// none sample

boolean isNone = pointer.isNone();

if (ignoreNone && isNone)

continue;

// value

Logic lv = pointer.logicValue();

if (invert)

lv = lv.invert();

if (swap)

lv = lv.swap();

// write changed value into array

int dim = inputDimension[n];

int offset = dimensionOffset[n];

for (int b = 0; b < dim; b++) {

byte v = lv.getState(b);

changed |= (hideIdentical && (v != value[dimension - 1 - (offset + b)]));

value[dimension - 1 - (offset + b)] = v;

}

// tag

boolean tag = keepTags && pointer.isTagged();

if (keepTags) {

boolean total = tagged > 0;

if (tag != tags[n]) {

tags[n] = tag;

tagged = tag ? tagged + 1 : tagged - 1;

}

changed |= (hideIdentical && (total != (tagged > 0)));

}

}

idx++;

}

}

// write

if (!hideIdentical || changed || !inital) {

((ILogicSamplesWriter) targetWriter).write(current, tagged > 0, (byte) ISample.STATE_0_BITS, value, 0, dimension);

inital = false;

}

32/64bit

32/64bit 32/64bit

32/64bit 32/64bit

32/64bit